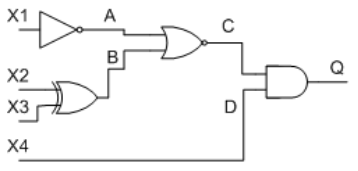

To jest dobry trop – bramka AND w tym przypadku rzeczywiście jest uszkodzona. Patrząc na układ na schemacie i porównując z tabelą pomiarów, można zauważyć ciekawą rzecz: wejścia C jest na stanie wysokim, D na niskim, czyli zgodnie z logiką, wyjście bramki AND powinno być niskie (bo AND daje wysoki tylko jeśli oba wejścia są wysokie). Ale w tabeli Q, czyli wyjście AND, jest wysokie! To już na pierwszy rzut oka nienaturalne dla układów cyfrowych – jeśli bramka AND daje wysoki przy jednym wejściu niskim, to coś ewidentnie nie gra. W praktyce branżowej, testowanie bramek polega właśnie na szukaniu takich nielogicznych sytuacji – to typowa procedura diagnostyczna, choćby w serwisowaniu sprzętu automatyki czy prostych systemów cyfrowych. Często spotyka się uszkodzenia, w których bramka „przepuszcza” wysoki stan mimo złych warunków wejściowych. Fajnie też wiedzieć, że takie nietypowe zachowanie może być przez chwilę niezauważone w prostych testach, dlatego zawsze warto sprawdzać stany wejść i wyjść krok po kroku. Moim zdaniem takie praktyczne przećwiczenie logiki to podstawa w automatyce, mikroprocesorach czy projektowaniu PCB. Gdybyś miał do czynienia z diagnozowaniem układów cyfrowych w praktyce (np. na warsztatach), to dokładnie takie przypadki się spotyka – czasem bramka jest „przebita” i daje sygnał logicznie sprzeczny z układem. Podsumowując: dobrze rozpoznany problem, a takie myślenie naprawdę przydaje się w branży, bo pozwala szybko wyłapywać usterki, zanim popsują one większy system.

Analizując układ i stan logiczny wszystkich punktów pomiarowych, warto dobrze zrozumieć działanie poszczególnych bramek w tego typu schematach. Wiele osób myli się, sądząc, że problem leży w bramkach XOR, NOT czy NOR, bo są one mniej intuicyjne niż AND. Jednak gdy popatrzymy na stan wejść i wyjść, łatwo zauważyć, że to nie one generują nielogiczny sygnał. Przykładowo: wejście A (za NOT) jest niskie, co oznacza, że NOT działa prawidłowo – jeśli X1 jest wysoki, to na wyjściu NOT stan powinien być niski i to się zgadza. Tak samo XOR: na wejściach B i A są odpowiednio niski i niski, a na wyjściu C mamy wysoki. XOR przy dwóch stanach niskich daje wynik niski, więc tu już coś nie gra, ale problem jest głębiej. NOR z kolei nie jest obecny fizycznie w tym fragmencie układu, więc wskazywanie tej bramki to często błąd wynikający z nieuważnego czytania pytania albo automatycznego kojarzenia z problemami w innych zadaniach. Największym, typowym błędem myślowym jest ignorowanie „klasycznych” usterek AND – wiele osób zakłada, że najbardziej skomplikowana bramka musi być winna, a tymczasem to właśnie podstawowa bramka AND może się „przepalić” czy ulec uszkodzeniu, zwłaszcza w starszych układach TTL czy CMOS (znam to z własnego doświadczenia). Jeśli logiczny stan Q jest wysoki przy jednym wejściu niskim (co powinno skutkować niskim na wyjściu AND), to jest to ewidentny dowód na uszkodzenie tej właśnie bramki. W praktyce przemysłowej testowanie i diagnozowanie polega na spokojnej analizie, krok po kroku, nie na szukaniu winnego po omacku. Branżowe dobre praktyki uczą, żeby zawsze porównywać stany logiczne na wejściach i wyjściach, nie pomijać prostych rozwiązań i ufać podstawowej logice cyfrowej. W tym przypadku poprawne zdiagnozowanie usterki wymagało tylko świadomego przeanalizowania tabeli pomiarowej i znajomości podstaw działania bramek AND, a nie szukania problemów tam, gdzie ich nie ma.