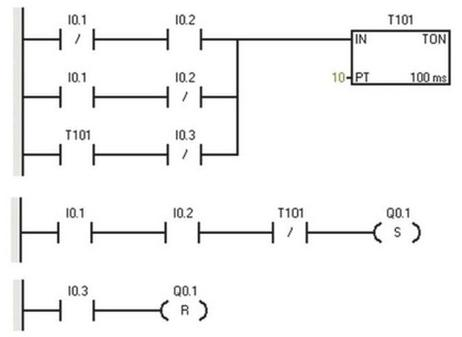

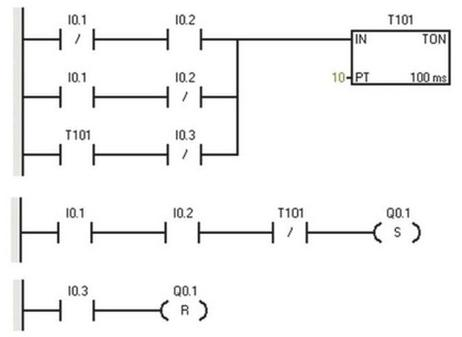

Aby wymusić stan wysoki na wyjściu Q0.1, konieczne jest jednoczesne aktywowanie obu wejść: I0.1 i I0.2. To działanie jest zgodne z zasadami działania bistabilnych wyjść, takich jak te wykorzystywane w programowalnych sterownikach logicznych (PLC). Wejście I0.1 działa jako cewka set (S), co oznacza, że jego aktywacja prowadzi do ustawienia wyjścia Q0.1 w stan wysoki. Z kolei I0.2, będące cewką reset (R), ma za zadanie resetować to wyjście. Kluczowym aspektem pracy z takimi układami jest zrozumienie opóźnień timera, który w tym przypadku wynosi 100 ms. Ustalając stan wysoki na wejściu I0.2 na krótszy czas niż 100 ms, nie aktywujemy cewki resetującej, co pozwala na bezpieczne ustawienie Q0.1 w stan wysoki. W praktyce, taka logika może być wykorzystywana w automatyce przemysłowej, gdzie konieczne jest jednoczesne włączanie i wyłączanie określonych funkcji w maszynach, co zwiększa efektywność procesów produkcyjnych. Dostosowanie parametrów czasowych oraz sposobu aktywacji wejść jest kluczowe dla optymalizacji działania systemów. Właściwe zrozumienie tych zasad pozwala na tworzenie bardziej złożonych i efektywnych programów sterujących.

Aktywizacja wyjść I0.1 i I0.2 z opóźnieniami lub w zbyt krótkich odstępach czasowych prowadzi do nieprawidłowego działania wyjścia Q0.1, co jest kluczowym zagadnieniem w programowaniu sterowników PLC. Ustawiając stan wysoki na I0.1 przez 1 sekundę, zakładamy, że system zdąży zignorować potencjalne konflikty wynikające z jednoczesnego aktywowania I0.2. Taki błąd myślowy wprowadza w błąd, ponieważ aktywacja I0.2 jako cewki resetującej powoduje, że Q0.1 zostanie zresetowane, co prowadzi do nieosiągnięcia pożądanego stanu wysokiego. Użytkownicy często mają tendencję do mylenia długości czasu aktywacji z samym momentem aktywacji. Przykładem może być myślenie, że ustawienie I0.2 na wysoki stan przez 1 sekundę po aktywacji I0.1 jest wystarczające, ale w rzeczywistości reset aktywuje się natychmiastowo, co prowadzi do odwrotnego efektu. Właściwe zarządzanie stanami i czasami w programowalnych układach logicznych jest kluczowe, aby uniknąć takich sytuacji w praktyce. W automatyce, gdzie czas reakcji jest krytyczny, konieczne jest zrozumienie, jak różne wejścia i wyjścia oddziałują na siebie oraz jakie są ich wzajemne zależności. Dlatego tak ważne jest przemyślane podejście do projektowania logiki, które zminimalizuje ryzyko niezamierzonych efektów w działaniu systemów.