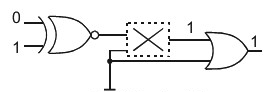

Bramka NAND to jeden z podstawowych elementów w cyfrowych układach logicznych. Działa na zasadzie negacji bramki AND, co oznacza, że jej wyjście jest w stanie logicznym 0 tylko wtedy, gdy oba wejścia mają stan 1. W przypadku tego zadania, gdy jedno wejście ma stan 0, a drugie 1, bramka NAND generuje na wyjściu stan 1. W praktycznych zastosowaniach bramki NAND są wykorzystywane w projektowaniu złożonych układów cyfrowych, takich jak rejestry czy układy pamięci. Zastosowanie tej bramki w układzie logicznym pozwala na efektywne tworzenie bardziej złożonych funkcji logicznych, ponieważ bramki NAND mogą być używane do budowy wszystkich innych typów bramek logicznych, co jest zgodne z zasadą uniwersalności. Warto zauważyć, że w standardach projektowania układów cyfrowych, bramki NAND są preferowane ze względu na ich prostotę i efektywność w implementacji różnych funkcji logicznych. Dlatego umieszczenie bramki NAND w miejscu oznaczonym X jest kluczowe dla uzyskania pożądanego wyniku na wyjściu.

Wybór bramki AND w tym przypadku prowadzi do nieprawidłowego rozumienia działania bramek logicznych i ich zastosowania. Bramka AND generuje stan logiczny 1 tylko wtedy, gdy oba jej wejścia są w stanie 1. W sytuacji, gdy jedno z wejść ma stan 0, wyjście bramki AND również będzie 0, co jest sprzeczne z wymaganym wynikiem 1. Zrozumienie działania bramki AND jest kluczowe, ale zastosowanie jej w tym układzie jest niewłaściwe, ponieważ nie spełnia warunków zadania. Ponadto, wybór bramki OR również jest błędny, ponieważ ta bramka daje na wyjściu stan 1, gdy przynajmniej jedno z wejść jest w stanie 1, ale w kontekście układu, w którym potrzebujemy bramki do przetwarzania stanów logicznych, jej zastosowanie nie prowadzi do dostarczenia wymaganego wyniku z uwagi na obecność bramki NOT w dalszej części układu. Kolejną błędną odpowiedzią jest bramka Ex-OR, która generuje stan 1 tylko wtedy, gdy wejścia są różne. W przypadku zadania, gdy jedno wejście jest w stanie 0, a drugie w stanie 1, wynik będzie 1, ale nie jest to rozwiązanie zgodne z wymaganiami układu, który opiera się na logice NAND, a nie na logice różnicowej. Stąd, kluczowym błędem jest nieuwzględnienie, że bramka NAND umożliwia uzyskanie pożądanego wyniku w sposób efektywny, co jest istotne w kontekście projektowania i analizy układów cyfrowych.