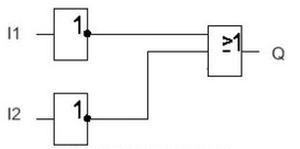

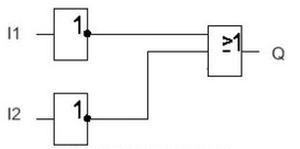

Układ przedstawiony na schemacie realizuje funkcję logiczną NAND. W istocie, składa się on z dwóch bramek: pierwszej, typu AND, oraz drugiej, będącej negacją wyjścia z bramki AND. Taki układ przyjmuje dwa wejścia (I1 i I2) i produkuje wyjście, które jest 0 tylko wtedy, gdy oba wejścia są w stanie 1. W przeciwnym razie, wyjście wynosi 1. Funkcja NAND jest istotna w cyfrowych układach logicznych, ponieważ może być wykorzystana do budowy wszystkich innych podstawowych bramek logicznych, takich jak AND, OR, czy NOT. Dzięki temu, bramki NAND znajdują szerokie zastosowanie w projektowaniu złożonych układów cyfrowych, w tym mikroprocesorów i układów FPGA. W praktyce, możliwość zrealizowania dowolnej funkcji logicznej przy użyciu jedynie bramek NAND czyni je niezwykle wszechstronnymi i popularnymi w inżynierii elektronicznej. Dodatkowo, w kontekście minimalizacji obwodów, wykorzystanie bramek NAND pozwala na oszczędność miejsca i zasobów, co jest kluczowe w nowoczesnych projektach elektronicznych.

Wybór odpowiedzi NOR, NAND, AND lub OR odzwierciedla zrozumienie podstawowych bramek logicznych, jednak wiele osób ma tendencję do mylenia ich funkcji, co prowadzi do błędnych wniosków. Na przykład, bramka NOR wytwarza wyjście 1 tylko wtedy, gdy oba wejścia są w stanie 0, co diametralnie różni się od funkcji NAND. Prowadząc do takiego błędu myślowego można zauważyć, że niektóre osoby mogą nie zwracać uwagi na połączenie bramek, co jest kluczowe w interpretacji schematów. W przypadku odpowiedzi AND, ważne jest zrozumienie, że ta bramka produkuje wyjście 1 tylko wtedy, gdy oba wejścia są w stanie 1. Stąd, jeśli jedno z wejść jest w stanie 0, wyjście również będzie 0, co jest sprzeczne z logiką NAND. Odpowiedź OR, z kolei, wydaje się bardziej intuicyjna, ponieważ wiele osób może sądzić, że połączenie dwóch wejść w taki sposób zawsze da aktywne wyjście, kiedy przynajmniej jedno z wejść jest aktywne. Jednak, schemat wyraźnie ilustruje, że wyjście z AND jest negowane, co sprawia, że funkcja logiczna zmienia się i nie może być po prostu interpretowana jako OR. Kluczowym aspektem do zapamiętania jest, że każda z tych bramek ma swoje specyficzne warunki działania, które muszą być dokładnie zrozumiane, aby uniknąć błędów w analizie układów logicznych.