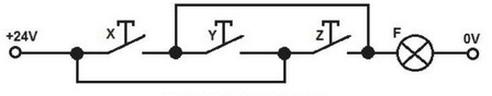

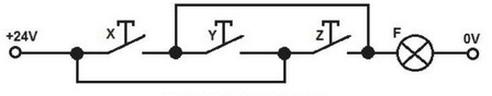

Poprawna odpowiedź F = X + Y + Z odnosi się do układu stykowego, który realizuje funkcję logiczną sumy. W układzie równoległym, takim jak przedstawiony na rysunku, obwód będzie zamknięty, gdy przynajmniej jeden z trzech styków (X, Y, Z) jest aktywowany. W praktyce oznacza to, że jeśli jakikolwiek z tych styków jest zamknięty, funkcja F przyjmuje wartość 1, co odpowiada stanowi 'prawda' w logice cyfrowej. Funkcje logiczne tego typu są często wykorzystywane w projektowaniu układów elektronicznych, takich jak systemy alarmowe czy układy sterowania, gdzie kluczowe jest monitorowanie stanu wielu źródeł sygnałów. Zgodnie z praktykami inżynierskimi, stosowanie sumy logicznej w takich aplikacjach pozwala na elastyczne łączenie różnych urządzeń, co zwiększa niezawodność systemu. Dodatkowo, w zastosowaniach automatyki przemysłowej, takie funkcje mogą być implementowane w programowalnych kontrolerach logicznych (PLC), co potwierdza ich znaczenie w nowoczesnym projektowaniu systemów automatyki.

Niewłaściwe odpowiedzi, takie jak F = Y · (X + Z), F = Y + X · Z oraz F = X · Y · Z, bazują na niepoprawnym zrozumieniu zasad działania układów stykowych. W przypadku funkcji Y · (X + Z), przyjmuje się, że wyjście F jest aktywne tylko wtedy, gdy styk Y jest zamknięty oraz przynajmniej jeden z pozostałych styków X lub Z również jest zamknięty. Taki układ logiczny nie może być realizowany w typowym połączeniu równoległym, gdzie jakiekolwiek zamknięcie styku powinno aktywować wyjście. Podobnie, konstrukcja F = Y + X · Z sugeruje, że aktywny stan F wymaga zarówno aktywacji styku Y, jak i jednoczesnego zamknięcia dwóch pozostałych styków, co jest sprzeczne z zasadą funkcji sumy logicznej. Wreszcie, funkcja F = X · Y · Z wskazuje na połączenie szeregowe, co oznacza, że wszystkie styki muszą być jednocześnie zamknięte, aby obwód był aktywny. Tego rodzaju myślenie prowadzi do błędnych wniosków, ponieważ w układzie równoległym kluczowe jest, aby przynajmniej jeden styk był zamknięty, co nie znajduje odzwierciedlenia w tych funkcjach. Zrozumienie różnic pomiędzy połączeniem szeregowym a równoległym jest kluczowe w analizie układów logicznych i projektowaniu systemów elektronicznych.