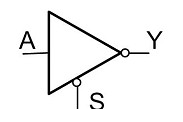

Bramka trójstanowa, znana również jako bramka Z, jest kluczowym elementem w projektowaniu układów cyfrowych, szczególnie w kontekście magistral danych. Posiada trzy stany wyjściowe: wysoki (logiczna 1), niski (logiczna 0) oraz stan wysokiej impedancji, który jest używany do odseparowania elektrycznego od reszty układu. Taki stan tożsamy jest z brakiem aktywnego sygnału na wyjściu bramki, co pozwala na współdzielenie linii komunikacyjnych przez wiele urządzeń. W praktyce, bramki trójstanowe są często wykorzystywane w konstrukcjach układów scalonych oraz w systemach komunikacji, gdzie wymagane jest zarządzanie przepływem informacji. Na przykład, w mikroprocesorach bramki trójstanowe pozwalają na kontrolowanie, które urządzenie na magistrali ma dostęp do danych, co zwiększa efektywność i elastyczność systemów. Zastosowanie bramek trójstanowych jest zgodne z zasadami projektowania systemów cyfrowych, gdzie kluczowe jest minimalizowanie zakłóceń oraz zapewnienie niezawodności przesyłania sygnału.

Niepoprawne odpowiedzi, takie jak NOT, jednostanowa oraz OR, odzwierciedlają nieporozumienia w zakresie zrozumienia funkcji oraz charakterystyki bramek logicznych. Bramki NOT, znane również jako negatory, mają tylko jeden stan wyjściowy, który jest odwrotnością stanu wejściowego – oznacza to, że nie są one w stanie odseparować sygnałów, lecz jedynie je przekształcać. Z kolei bramka jednostanowa to termin, który nie jest powszechnie używany w kontekście logiki cyfrowej, co może wprowadzać w błąd. Bramki OR, z drugiej strony, służą do realizacji operacji logicznej OR, gdzie na wyjściu pojawia się sygnał wysoki, jeśli przynajmniej jedno z wejść jest w stanie wysokim. Takie podejście nie zapewnia jednak stanu wysokiej impedancji, co jest kluczowe w kontekście odseparowania elektrycznego. Błędem myślowym, który prowadzi do wyboru tych odpowiedzi, jest nieodróżnianie bramek cyfrowych na podstawie ich funkcji oraz nieuznawanie, że bramka trójstanowa pełni unikalną rolę w zarządzaniu sygnałem w porównaniu do innych rodzajów bramek. Właściwe zrozumienie charakterystyki bramek logicznych jest kluczowe dla efektywnego projektowania układów cyfrowych oraz zapewnienia ich prawidłowego działania.